Famílias Lógicas

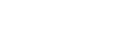

As portas lógicas e circuitos lógicos mais complexos são fornecidos pela indústria como Circuitos Integrados(CIs) digitais. CIs digitais são um conjunto de resistores, diodos, capacitores e transistores fabricados sobre o mesmo substrato de material semicondutor(geralmente, sílicio), cuja denominação comum é chip. Os chips são encapsulados em envólucros de plástico ou cerâmica, com pinos metálicos para conexão dos CIs com outros dispositivos.Um dos tipos mais comum de envólucros é o dual-in-line (DIP) mostrado na Fig.1.

Fig.1

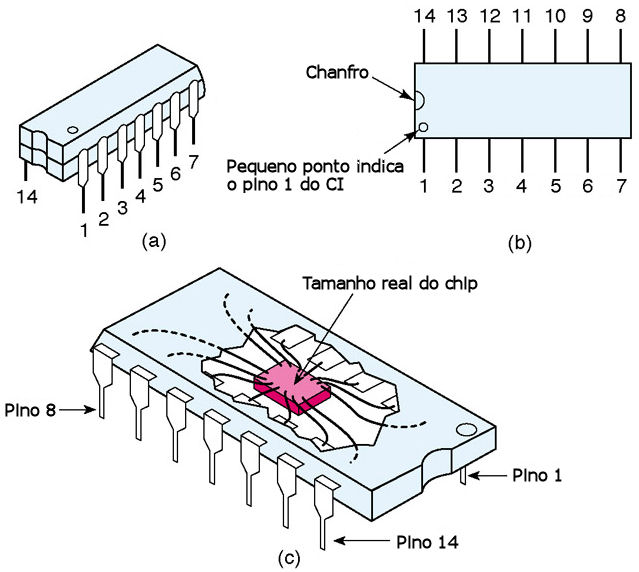

Os CIs digitais são classificados de acordo com sua complexidade, medida pela quantidade de portas lógicas no substrato. Atualmente, existem seis níveis de complexidade que estão mostrados na tabela da Fig.2

Fig.2

Nos sistemas digitais atuais, os CIs MSI e de integração em larga escala( LSI, VLSI, ULSI, GSI) realizam a maioria das funções que antes eram realizadas por circuitos com vários CIs SSI. Contudo, os chips SSI são usados com 'interface' ou 'grude' entre os CIs mais complexos

CIs Digitais Bipolares e Unipolares

Os CIs digitais podem ser classificados também pelo tipo de componente eletrônico empregado nos seus circuitos.

Nos últimos 45 anos, a família TTL(Transistor-Transistor Logic) foi a principal família de CIs digitais. A série 74 - comercial de aplicação civil - foi a primeira série da família TTL.Hoje a série 74 é usada como padrão de comparação embora não seja empregada em projetos modernos.A Fig.3a mostra o circuito de uma porta INVERSOR TTL contendo vários transistores bipolares.

Fig.3

A família TTL perdeu a liderança nas categorias de CIs SSI e MSI para a família CMOS(Complementary Metal-Oxide -Semiconductor). A família CMOS usa transistores unipolares MOSFET de canal N e canal P como elemento principal no circuito. A Fig.3 mostra uma porta INVERSOR CMOS padrão.

Família TTL

A família TTL é constituída de várias série, conforme a tecnologia com que são fabricadas e suas características técnicas. A tabela da Fig.4 relaciona cada série com o prefixo usado para identificar o CI como pertencente a determinada série.

Fig.4

O prefixo 74 identifica os CIs TTL comerciais, para aplicação civil. Os CIs TTL de aplicação militar são identificados pelo prefixo 54 e não são disponíveis comercialmente.As diferenças entre as séries TTL são definidas por suas caracterísiticas elétricas como dissipação de potência, tempos de propagação, velocidade de comutação. Não há diferenças na disposição dos pinos ou na operação lógica realizada pelos circuitos internos.

Família CMOS

A tabela da Fig.5 resume as várias sub-famílias CMOS disponíveis. A série 4000 é a mais antiga das séries CMOS. ela apresenta várias das funções lógicas da família TTL, porém não é compatível pino a pino com os CIs TTL. As séries 74C, 74HC, 74HCT, 74AC e 74ACT são as mais novas da família CMOS. As três primeiras séries, 74C, 74HC, 74HCT, são compatívieis pino a pino com os CIs TTL correspondentes. As séries 74HC, 74HCT operam a velocidades maiores que os CIs da série 74C. A série 74HCT é eletricamente compatível com os CIs TTL, podendo ser conectados entre si sem qualquer circuito de interface. As séries 74AC e 74ACT são CIs de alto desempenho e não são compatíveis pino a pino com TTL. Os CIs 74ACT são eletricamente compatíveis com TTL.

Fig.5

Alimentação e Terra

Em circuitos TTL, o pino de alimentação é chamado VCC. Nos circuitos CMOS, o pino de alimentação é chamado de VDD. Como muitos CIs CMOS são empregados juntos com TTL, então VCC também é usado para designar o pino de alimentação desses CIs CMOS.

Faixas de Tensão para Níveis Lógicos

Para CIs TTL, VCC deve ser igual a +5V. Para CIs CMOS, a tensão de alimentação VDD pode estar na faixa de +3 a +18V, embora +5V seja a tensão mais usada, principalmente quando CMOS está sendo empregada no mesmo circuito que TTL.

Para os CIs TTL padrões, as tensões de entrada aceitáveis para os níveis lógicos 0 e 1 estão mostradas na Fig.6. Nível lógico 0 é qualquer tensão na faixa de 0 a 0,8V; e qualquer tensão na faixa de 2,0 a 5,0V é considerada nível lógico 1.Tensões que não estão dentro destas faixas são consideradas indeteminadas e os fabricantes não garantem o funcionamento lógico correto do CI para tensões indeteminadas.

Fig.6

A Fig.6b mostra as faixas de tensão para os níveis lógicos 0 e 1 dos CIs CMOS com tensão de alimentaçãoVDD igual a +5V. Tensões entre 0 e 1,5V são reconhecidas como nível lógico 0, e tensões entre 3,5 e 5V são definidas como nível lógico 1. As tensões entre 1,5 e 3,5V são indeterminadas e os circuitos não respondem corretamente a estas tensões.

Entradas Não-Conectadas

Uma entrada de um CI não conectada é chamada de entrada em flutuação. Uma entrada TTL em flutuação funciona como se estivesse conectada ao nível lógico 1. Porém, entradas em flutuação são bastante sensíveis a ruídos e não devem ser deixadas em flutuação.

Uma entrada de um CI CMOS em flutuação pode aquecer o CI e danificar os circuitos internos do chip. Assim, todas as entradas de CIs CMOS devem ser ligadas ao nível ALTO ou BAIXO, ou a saída de outro CI. A tensão medida em uma entrada CMOS em flutuação varia em função do ruído presente, causando uma oscilação na tensão de saída do CI.

Características da Série TTL Padrão

A linha de CIs TTL 54/74, introduzida em 1964, pela Texas Instruments, é a série mais popular de CIs digitais. A série 54, de aplicações militares, podem operar em temperaturas e tensões maiores que a série 74. Os maiores fabricantes de CIs produzem chips TTL, mudando o prefixo porém mantendo a numeração do dispositivo.

Faixas de Tensão de Alimentação e de Temperatura

As séries 54/74 usam uma tensão de alimentação nominal de 5V(VCC). A série 74 opera de modo confiável na faixa de 4,75 a 5,25V, e a série 54 pode usar uma faixa de 4,5 a 5,5V. As temperaturas de operação podem variar de 0 a 70ºC para CIs 74, enquanto a série 54 suporta temperaturas de -55 a +125ºC.

Níveis de Tensão

Os níveis de tensão lógicos de entrada e saída para a série TTL padrão podem ser vistas na Fig.7.

Fig.7

Observe que o nível lógico 0 de saída VOL=0,4V é 400mV menor que a tensão de nível lógico 0 necessária na entrada, VIL=0,8V. A diferença de VIL menos VOL é a margem de ruído garantida no nível lógico 0. Do mesmo modo, a saída em nível lógico 1, VOH, garantida é 2,4V, que é 400mV maior que a tensão de entrada necessária em nível lógico 1, VIH=2,0V. Assim, a margem de ruído CC, VOH-VIH, é 400mV para o estado ALTO.

Faixas Máximas de Tensão

As tensões aplicadas em qualquer entrada de CIs 74 padrão não devem exceder +5,5V.O limite de tensão negativa máxima que pode ser aplicado em uma entrada TTL é igual a -0,5V.

Disssipação de Potência

Uma porta NAND TTL padrão consome uma potência média de 10mW, que é o produto da corrente média consumida pelo CI, ICCm=ICCH-ICCL, vezes a tensão de alimentação VCC. A potência consumida por porta é igual a potência consumida pelo CI dividida pelo número de portas no chip.

Atrasos de propagação

A velocidade das portas lógicas é controlada pelo tempo que gasta para comutar de um nível lógico para outro. O tempo que leva para comutar os níveis lógicos é o atraso de propagação(tP) ou atraso da porta. As portas lógicas geralmente tem diferentes tempos para chavear de um nível lógico ALTO para BAIXO(tPHL), e comutar do nível lógico BAIXO para ALTO(tPLH). Em geral, se usa um tempo médio igual a média dos tempos de comutação ALTO para BAIXO(tPHL) e BAIXO para ALTO(tPLH). Para uma porta AND TTL padrão, tPHL=7ns e tPLH=11ns, resultando um atraso de propagação médio tP=9ns.

Capacidade de Saída( Fan-Out )

Capacidade de saída, Fan-Out, é o número máximo de entradas de portas que podem ser acionadas pela saída de uma porta. É calculada dividindo a corrente total acionadora de saída de corrente total de carga(acionada) de entrada. Uma porta TTL padrão tem um fan-out igual a 10. Como este parâmetro varia entre as séries, e os manuais não especificam, então o fan-out deve ser calculado em cada aplicação.

Saída Totem-Pole

Existem várias possibilidades para o estágio de saída de um dispositivo TTL.O tipo padrão do estágio de saída bipolar é mostrado na Fig.8a, de uma porta NAND TTL, com duas entradas A e B e uma saída.

Fig.8

A saída totem-pole é composta dos transistores Q3 e Q4, e diodo D1. Quando a saída está no nível lógico ALTO, Q3 está conduzindo e Q4 cortado.O transistor Q3 fornece a conexão de VCC para a saída. Para a saída no nível lógico BAIXO, o transistor Q3 está cortado e o transistor Q4 em condução. Neste caso, Q4 fornece a ligação da saída para o terra, produzindo nível lógico BAIXO. O diodo D1 é necessário para manter o transistor Q3 cortado nesta situação, pois 0,8V na base de Q3 não é suficiente para polarizar diretamente a junção base-emissor de Q3 e D1.

As saídas totem-pole de duas portas não devem ser curto-circuitadas, pois se uma estiver ALTA e outra BAIXA, há uma corrente excessiva da fonte para o terra que pode danificar os circuitos.

Saída Coletor-Aberto

A saída coletor-aberto é mostrada na Fig.9. Esta saída elimina o transistor Q3, o diodo D1 e o resistor R4. A saída é coletor de Q4 que está aberto. Para funcionar corretamente, um resistor de pull-up externo, RP, deve ser conectado. este resistor deve ser dimensionado e ligado pelo usuário e igual a 10KOhm.

Fig.9

Saída Tristate(Terceiro Estado ou Alta Impedância)

A configuração tristate permite operação de alta velocidade e que as saídas possam ser consctadas juntas. É denominada tristate porque proporciona três estados possíveis para uma saída de porta TTL: ALTO, BAIXO e alta impedância(Hi-Z). No estado de alta impedância, ambos transistores Q3 e Q4 estão cortados e o terminal de saída apresenta uma alta impedância pra o terra e VCC.A saída fica aberta ou flutuante, que não está nem ALTO nem BAIXO.

O circuito tristate é obtido através de uma entrada de HABILITAÇÃO(ENABLE) que produz o estado de alta impedância, conforme mostra a Fig.10.

Fig.10

Com a entrada de HABILITAÇÃO(E) no nível ALTO, E=1, não há qualquer modificação na operação do transistor Q1 e diodo D2, e o circuito funciona como um inversor com entrada A.

Um nível BAIXO na entrada de HABILITAÇÃO, E=0, polariza diretamente a junção base-emissor de Q1 e desvia toda corrente de R1 da base de Q2, cortando Q2 e provocando o corte de Q4. O nível BAIXO na entrada E polariza diretamente o diodo D2 que desvia toda corrente de base de Q3 e este transistor entra em corte.

Como ambos transistor estão sem conduzir, então o terminal de saída está praticamente em circuito aberto.

Embora a lógica TTL de 5V ainda tenha aplicação, novas tecnologias de baixa tensão estão sendo colocadas no mercado e estão deslocando a tecnologia de 5V.A Fig.11 mostra o ciclo de vida das várias famílias lógicas na visão da Texas Instruments.

Fig.11

Atualizada em 19/03/12