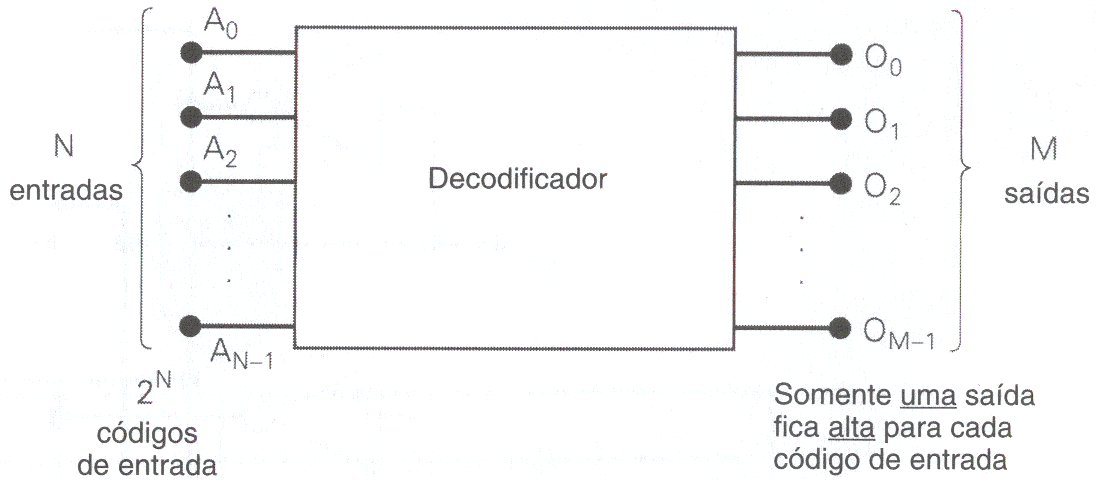

Decodificadores

Decodificador - circuito cujas entradas representam um número binário(código) e ativa apenas a saída correspondente ao número(código) na entrada. Todas as outras saídas permanecem inativas. O decodificador pode detetar um código e ativar um único sinal de saída na presença desse código. O código, que é o endereço da saída a ser ativada, pode ser apresentado ao decodificador como a saída de outro circuito lógico, tais como endereços de um microprocessador, ou de chaves e contatos.

Operações comumente realizadas em um sistema digital:

|

Alguns códigos não utilizam as 2n combinações de entrada, como o código BCD, neste caso, quando um código inválido aparece na entrada, então nenhuma linha de saída é ativada. Um decodificador é identificado pelo número de entradas de seleção para as saídas decodificadas, ou pelo número de entradas de seleção. Um decodificador com n entradas de seleção pode endereçar 2n saídas.

Decodificador 8-para-1(binário-para-octal)

Tabela Verdade

Equações Lógicas

Circuito Lógico

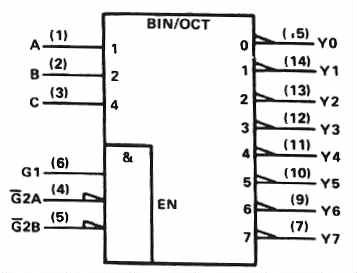

Circuito Integrado Decodificador SN74LS138

Características:

Todas as saídas são ativas BAIXAS, mutuamente excludentes.

Três entradas de HABILITAÇÃO G1, G2A, G2B, duas entradas G2A, G2B ativas

BAIXAS e uma entrada G1 ativa ALTA.

Três entradas de endereços A, B, C que fornecem, quando habilitado,

8 saídas ativas BAIXAS, mutuamente excludentes, Y0 até Y7.

| Circuito Lógico | Tabela Verdade | |||||||

|

|

|||||||

| Fig.3 | Fig.4 | |||||||

O símbolo lógico IEEE/ANSI para o decodificador 74LS138 incorpora um tipo de notação denominada notação de dependência.Os pinos de entrada estão à esquerda e os de saída à direita.Os números nas extremidades das linhas de entradas e saídas são os números dos pinos do CI.A indicação X/Y mostra que o CI é um decodificador.As entradas de endereços(código) têm pêsos 1, 2 e 4.A soma dos pêsos dos pinos de entrada (1), (2) e (3) ativos determina o número da linha de saída que é ativada.As saídas são ativas quando baixas.O retângulo marcado & e suas entradas G1, G2A, G2B e a denominação EN indicam que as linhas de entrada (4), (5) e (6) são combinadas em uma porta AND para produzir o sinal habilitador interno do CI.As entradas de habilitação (4) e (5) são ativas baixas e a (6) é ativa alta.

A folha de dados completa do CI decodificador SN74LS138 pode ser vista usando usando o Adobe Acrobat 7.0. Os decodificadores tem várias aplicações: as saídas ativadas podem servir para ativar o alarme de um sistema com uma ocorrência de uma combinação específica de entradas; partir um determinado sistema em resposta a uma combinação decodificada; servir como decodificador de um código específico de entrada para habilitar outro circuito; e ser empregado como sofisticado decodificador de endereços para ativar vários dispositivos tais como chips de memórias em um sistema microprocessado.

Estruturas em Árvore

Decodificadores podem ser cascateados para expandir o número de palavras códigos que podem ser decodificadas. As entradas de habilitação dos decodificadores são usadas para os bits mais significativos(MSBs) dos códigos quando mais de um decodificador são cascateados habilitando cada decodificador e os bits menos significativos do código são aplicados nas entradas dos decodificadores e ativam a saída correspondente.a figura abaixo mostra um decodificador de 5 entradas e 32 saídas com o CI 74LS138 e alguma lógica adicional.

| Decodificação de Endereço Binário-para-Octal | |||||

As entradas A, B, e C é um número binário aplicado nas entradas de seleção.As oito saídas Y0 até Y7 representam os oito caracteres do sistema octal, que são ativadas uma por vez em resposta ao endereço de entrada. |

|||||

|

|||||

| Fig.7 | |||||

| Decodificação de Endereço Binário-para-Hexadecimal |

|||||

| O CI SN74154 é um decodificador 4-para-16, projetado para realizar a decodificação de endereços binários para hexadecimal. Um número binário é a entrada das quatro entradas de seleção para ativar uma das dezesseis saídas. As 16 saídas individuais representam os 16 caracteres do sistema hexadecimal. Em qualquer instante um número binário de 4-bits é convertido para 1 de 16 sinais. |

|||||

|

|||||

Fig.8 |

|||||

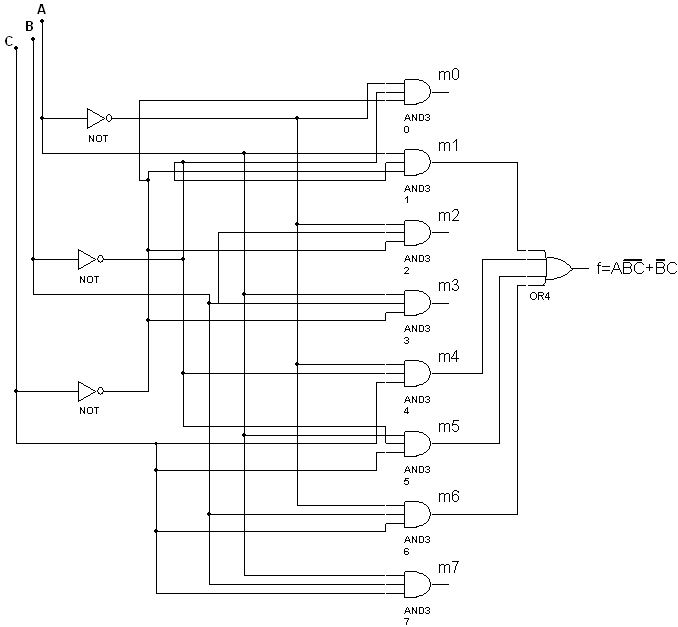

Gerador de Funções Lógicas

Decodificadores podem ser usados para gerar funções lógicas, acrescentando-se uma porta de saída ao CI decodificador para implementar a soma de produtos(SOP) da função lógica. Neste caso, cada saída do decodificador é um termo produto(mintermo) da função lógica especificada. A porta a ser acrescentada depende do circuito interno do decodificador e do número de mintermos necessários para representar a função. Se o circuito interno do decodificador é um arranjo de portas NAND e tem saídas ativas BAIXAS, então acrescenta-se uma porta NAND, com um número de entradas igual ao número de termos produtos da função, resultando numa estrutura NAND-NAND, que implementa a equação SOP(soma de produtos). Similarmente, se o circuito interno do decodificador é um arranjo de portas AND, e apresenta saídas ativas ALTAS, então uma porta OR, com número de entradas igual ao número de termos produtos da função, é colocada na saída para formar a estrutura AND-OR que implementa a função. Veja na Fig.9 um exemplo de geração de função lógica de três variáveis, empregando um decodificador de 3:8.

Fig.9

| Questões de Revisão Resolva as questões e problemas propostos no teste acima. |

Atualizada em 4/10/11