Problemas

1.Desenhe o circuito lógico de um codificador com prioridade com quatro entrada I3I2I1I0 e duas saídas A1A0. A entrada I3 deve ter prioridade sobre a entrada I2, a entrada I2 sobre a entrada I1 e I1 sobre I0. Inclua no projeto uma entrada de habilitação(EN), uma saída de habilitação(EO) para habilitar outro codificador e uma saída de sinal de grupo(GS) que deve ser ativa quando uma entrada estiver ativa. Todas as entradas e saídas devem ser ativas ALTAS e use a menor quantidade possível de portas.

Solução

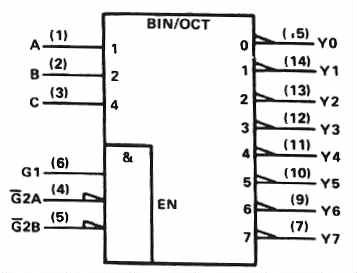

2.No circuito integrado 74138 da Fig.2, os pino (4) e (5) estão no nível L e ABCG1 são iguais à representação BCD do dígito menos significativo do seu CPF. Quais os níveis lógicos(L ou H) dos pinos de saída Y0 até Y7?

Solução

3.Utilizando somente o CI multiplexador 74AS151 mostrado na Fig.3 abaixo, complemente a Fig.2B de modo que a saída Y seja igual à função lógica das variáveis de entrada t, u, v, x e Y= f(t,u,v,x) é dada por

Y = f(t,u,v,x) = Σm(0,mi,5,6,9,10,12,15)

Considere mi igual ao terceiro menor dígito do seu CPF. Mostre todas as entradas e a saída na Fig.2B.

Solução

|

|

|

Fig.3A |

Fig.3B |

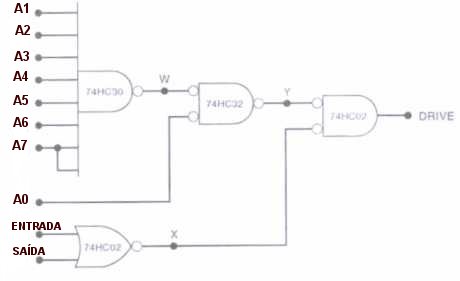

4.O circuito lógico da Fig.4 é usado para controlar o motor de uma unidade de disco quando o microcomputador está enviando ou recebendo dados do disco.O circuito ligará o motor quando DRIVE=1. Determine as condições de entradas necessárias para ligar o motor. Quais devem ser os valores de W, X e Y? Explique.

Solução

|

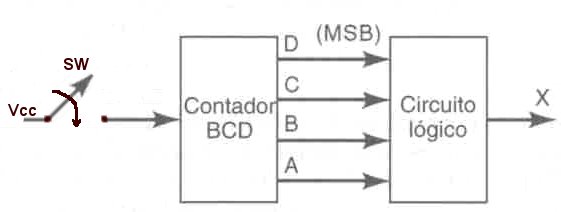

5.A Fig.5 mostra o diagrama em blocos de um circuito que produz uma saída de quatro bits, que representa, em código BCD, o número de vezes que a chave SW é fechada.Por exemplo, se chave SW fôr fechada quatro vezes, a saída do circuito é DCBA=01002=410. Após a chave ser fechada dez vezes, a saída volta para 0000 e a saída nunca será maior que 1001. Projete um circuito que forneça uma saída X em nível ALTO quando a chave fechar 2, 3, ou 9 vezes.Use somente portas AND e OR de duas entradas e NOT, e a menor quantidade possível de portas.

Solução

|

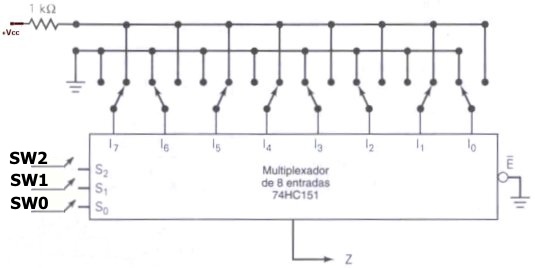

6.A Fig.6a mostra como um multiplexador pode ser usado para gerar uma forma-de-onda lógica de saída Z com um padrão desejado. O padrão é programado usando oito chaves nas entradas do multiplexador e a forma-de-onda é produzida fechando e abrindo as chaves SW2, SW1 e SW0.Considerando que as chaves SWs fechadas aplica nível lógico ALTO e abertas nível BAIXO, desenhe a forma-de-onda da saída Z.

Solução

|

|

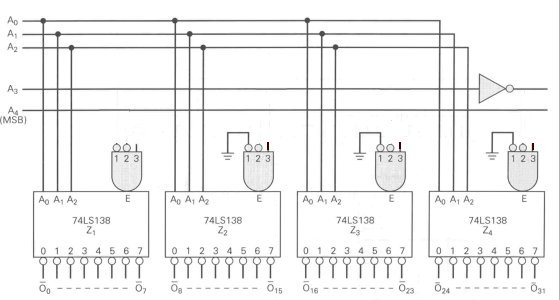

7.A Fig.7a mostra como quatro decodificadores 74LS138 e um inversor podem ser interligados para funcionarem como um decodificador de 5 para 32 com entradas A4A3A2A1A0 e saídas ativas BAIXAS O0 até O31. Sem utilizar quaisquer portas adicionais, complemente o projeto do decodificador.

Solução

|

|

8.O sistema de alarme de um carro é mostrado na Fig.8a abaixo.Empregando somente as portas mostradas na Fig.8b, re-projete o circuito de alarme.Mostre todas as ligações, entradas e saídas.(Desenhe na Fig.8b)

Solução

|

|

9.Um circuito lógico tem três entradas de dados A, B e C e duas saídas Y e Z. A saída Y será ALTA se um número par de 1s está presente na entrada de dados. A saída Z será ALTA se existe um número ímpar de 1s na entrada de dados .Desenhe o circuito empregando as portas mostradas na Fig.9. Mostre todas as ligações, entradas e saídas.

Solução

|

|

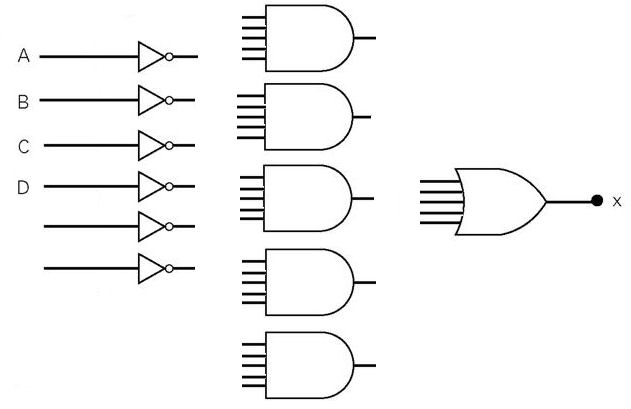

10.Empregando a menor quantidade possível de portas mostradas na Fig.10, complete o circuito de modo que a saída X seja dada pela expressão abaixo. Considere a varíavel A a mais significativa e D a variável menos siginificativa, e o índice i igual ao dígito menos significativo e j igual ao dígito mais significativo do número de seu CPF.

Solução

| A | B |

C |

D | X |

Fig.1

| 0 | 4 | 12 | 8 |

| 1 | 5 | 13 | 9 |

| 3 | 7 | 15 | 11 |

| 2 | 6 | 14 | 10 |

Atualizada em 3/04/12