2.4. INTERRUPCIONES DEL PROCESADOR

La siguiente figura muestra un ejemplo común de procesamiento de una interrupción. En un sistema de cómputo, una interrupción es un evento que altera la secuencia en que el procesador ejecuta las instrucciones. La interrupción es generada por el hardware del sistema de cómputo. Cuando ocurre una interrupción:

- El sistema operativo toma el control (es decir, el hardware pasa el control al sistema operativo).

- El sistema operativo guarda el estado del proceso interrumpido. En muchos sistemas esta información se guarda en el bloque de control de proceso interrumpido.

- El sistema operativo analiza la interrupción y transfiere el control a la rutina apropiada para atenderla; en muchos sistemas actuales el hardware se encarga de esto automáticamente.

- La rutina del manejador de interrupciones procesa la interrupción.

- Se restablece el estado del proceso interrumpido (o del "siguiente proceso").

- Se ejecuta el proceso interrumpido (o el "siguiente proceso")

Una interrupción puede ser iniciada específicamente por un proceso en ejecución (en cuyo caso se suele denominar trampa (frap), y se dice que está sincronizada con la operación del proceso) o puede ser causada por algún evento que puede estar relacionado o no con el proceso en ejecución (en cuyo caso se dice que es asíncrona con la operación del proceso).

Una ventaja importante de las interrupciones es que son una forma económica de llamar la atención de la UCP, de modo que la UCP no necesita escrutar constantemente los dispositivos para ver si alguno requiere atención.

Un ejemplo simple de la diferencia entre escrutinio e interrupción se puede observar en las cocinas modernas equipadas con hornos de microondas. El cocinero puede ajustar un reloj para que se detenga después de cierto tiempo (un ejemplo de interrupción es el sonido que produce la alarma cuando transcurre el tiempo), o bien, el cocinero puede mirar periódicamente a través de la ventana del homo para ver cómo se cocina el asado (esta clase de vigilancia periódica es un ejemplo de escrutinio).

Los sistemas orientados hacia las interrupciones pueden sobrecargarse. Si éstas llegan con mucha frecuencia, el sistema no será capaz de atenderlas. Un controlador humano de tráfico aéreo podría verse fácilmente abrumado si convergieran muchos aviones en una zona reducida. En algunos sistemas orientados hacia el teclado, cada tecla presionada almacena en la memoria un código de un byte y genera una interrupción para informar a la UCP que un carácter está listo para ser procesado. Si la UCP no puede procesar el dato antes de que se presione la siguiente tecla, se pierde el primer carácter.

Clases de interrupciones

- En esta sección y en la siguiente se trata el esquema de interrupciones de los procesadores a gran escala de IBM. Existen seis clases de interrupciones:

- Interrupciones SVC (supervisor cali, llamadas al supervisor). Son iniciadas por un proceso en ejecución que ejecute la instrucción SVC. Una SVC es una petición generada por el usuario de un servicio particular del sistema, como realizar una operación de entrada/salida, obtener más memoria o comunicarse con el operador del sistema. El mecanismo de las SVC ayuda a proteger el sistema operativo de las acciones de los usuarios. Un usuario no puede entrar arbitrariamente al sistema operativo, sino que debe solicitar un servicio por medio de una SVC. El sistema operativo está al tanto de todos los usuarios que intentan rebasar sus límites y puede rechazar ciertas peticiones si el usuario no tiene los privilegios necesarios.

- Interrupciones de E/S. Son iniciadas por hardware de entrada y salida. Estas interrupciones indican a la UCP el cambio de estado de un canal o un dispositivo. Las interrupciones de E/S se producen cuando finaliza una operación de E/S o cuando un dispositivo pasa al estado listo, por ejemplo.

- Interrupciones externas. Son causadas por diversos eventos, incluyendo la expiración de un cuanto de un reloj que interrumpe, la pulsación de la tecla de interrupción de la consola o la recepción de una seńal procedente de otro procesador en un sistema de múltiples procesadores.

- Interrupciones de reinicio. Ocurren cuando se presiona el botón de reinicio de la consola o cuando llega desde otro procesador una instrucción de reinicio SIGP (seńal del procesador) en un sistema de múltiples procesadores.

- Interrupciones de verificación del programa. Son causadas por una amplia clase de problemas que pueden ocurrir cuando se ejecutan las instrucciones en lenguaje de máquina de un programa. Dichos problemas incluyen la división entre cero, el exceso o defecto de los números que pueden ser manejados por las operaciones aritméticas, la presencia de datos (con los cuales se está trabajando) con un formato erróneo, el intento de ejecutar un código de operación inválido, el intento de hacer referencia a una localidad de memoria que esté fuera de los límites de la memoria real, el intento por parte de un proceso de usuario de ejecutar una instrucción privilegiada y el intento de hacer referencia a un recurso protegido. Muchos sistemas ofrecen a los usuarios la opción de especificar las rutinas que deben ejecutarse cuando ocurra una interrupción de verificación del programa.

- Interrupciones de verificación de la máquina. Son ocasionadas por el mal funcionamiento del hardware.

Cambio de contexto

En el esquema de interrupciones de los procesadores a gran escala de IBM, el sistema operativo incluye rutinas denominadas manejadores de interrupciones de primer nivel (first level interrupt handiers, FLIH) para procesar las diferentes clases de interrupciones. Por tanto, hay seis manejadores de interrupciones de primer nivel: FLIH de SVC, FLIH de E/S, FLIH externo, FLIH de reinicio, FLIH de verificación del programa y FLIH de verificación de la máquina. Cuando ocurre una interrupción, el sistema operativo guarda el estado del proceso interrumpido y transfiere el control al manejador de interrupciones de primer nivel apropiado. Esto se logra mediante una técnica llamada cambio de contexto (Lm68). Los manejadores de interrupciones de primer nivel deben distinguir entre interrupciones de la misma clase; el procesamiento de estas interrupciones es realizado entonces por alguno de los manejadores de interrupciones de segundo nivel.

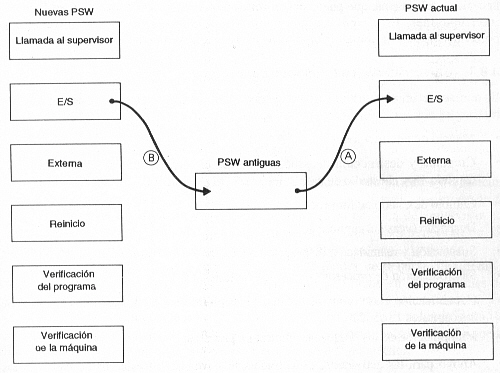

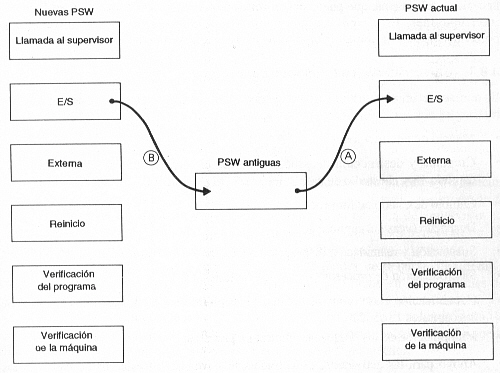

Las palabras de estado del programa (program status \vords, PSW) controlan el orden de ejecución de las instrucciones y contienen información acerca del estado de un proceso. Hay tres tipos de PSW: PSW actuales, PSW nuevas y PSW antiguas.

La dirección de la siguiente instrucción que se debe ejecutar se almacena en la PSW actual, que indica también los tipos de interrupciones habilitadas e inhabilitadas en ese momento. La UCP permite que ocurran las interrupciones habilitadas; las interrupciones inhabilitadas permanecen pendientes o, en algunos casos, se pasan por alto. El procesador nunca puede estar inhabilitado para una interrupción SVC, para una de reinicio o para algunos tipos de interrupciones de programa. Posteriormente se explicarán las razones para habilitar o inhabilitar interrupciones.

En un sistema de un procesador sólo hay una PSW actual, pero hay seis PSW nuevas (una para cada tipo de interrupción) y seis PSW antiguas (de nuevo, una para cada tipo de interrupción). La PSW nueva para algún tipo de interrupción contiene la dirección permanente de la memoria principal en la que reside el manejador de interrupciones correspondiente. Cuando ocurre una interrupción, si el procesador no está inhabilitado para ese tipo de interrupción, el hardware automáticamente cambia las PSW como sigue:

- se guarda la PSW actual en la PSW anterior de este tipo de interrupción,

- se guarda la PSW nueva de este tipo de interrupción en la PSW actual.

Después de este intercambio de PSW, la PSW actual contendrá la dirección del manejador de interrupciones apropiado. Éste ejecuta y procesa la interrupción.

Cuando se completa el procesamiento de la interrupción, se asigna la UCP el proceso que se estaba ejecutando cuando ocurrió la interrupción o bien al proceso listo con mayor prioridad. La elección depende de si el proceso interrumpido es apropiable o no apropiable. Si el proceso no es apropiable, recupera la UCP; si el proceso es apropiable, recuperará la UCP sólo si no hay más procesos listos.

Hay muchos esquemas de interrupción importantes, diferentes del que se acaba de describir. Un esquema de interrupción que ha sido muy utilizado se denomina interrupciones con vectores completos. En este esquema, cada interrupción individual hace que se guarde un código de interrupción único. Existe un vector de interrupciones que es en esencia un arreglo de direcciones almacenado en memoria. Los índices del arreglo corresponden a los códigos de interrupción individuales. Los elementos del arreglo contienen las direcciones en las cuales se encuentran los manejadores de interrupciones para cada uno de los códigos de interrupción.

INTERCAMBIO DE LA PSW